### Class-D amplifiers are

becoming key components of low power modern consumer devices. Their high efficiency makes them ideal audio amplifiers in laptops, cell-phones, subwoofers, and other mobile audio devices. This VLSI project implements the signal processing "front end" component of a class-D amplifier. The inputs to the circuit are stereo line-in audio, and the outputs are designed to drive an H-bridge for each audio channel. Volume control has also been implemented as a five-bit digital number input.

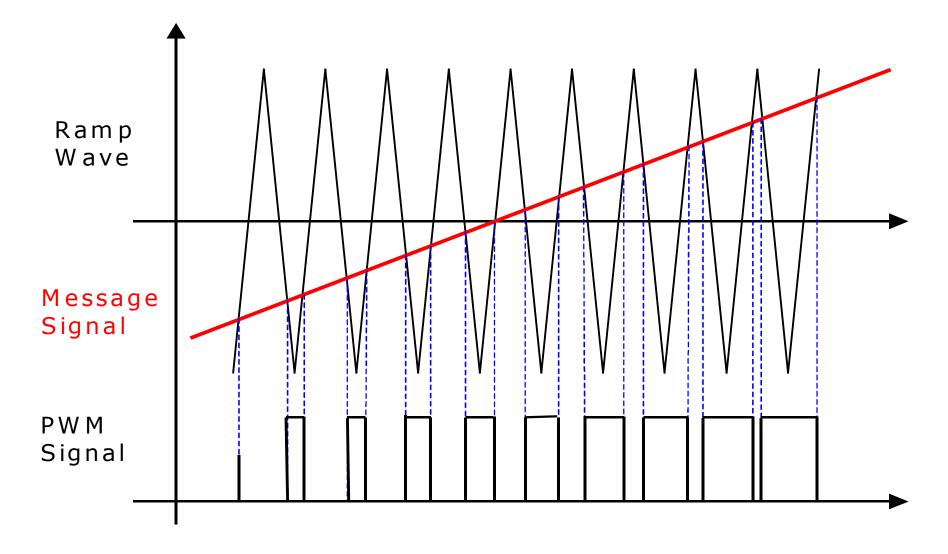

Theory of pulse-width modulation (PWM)

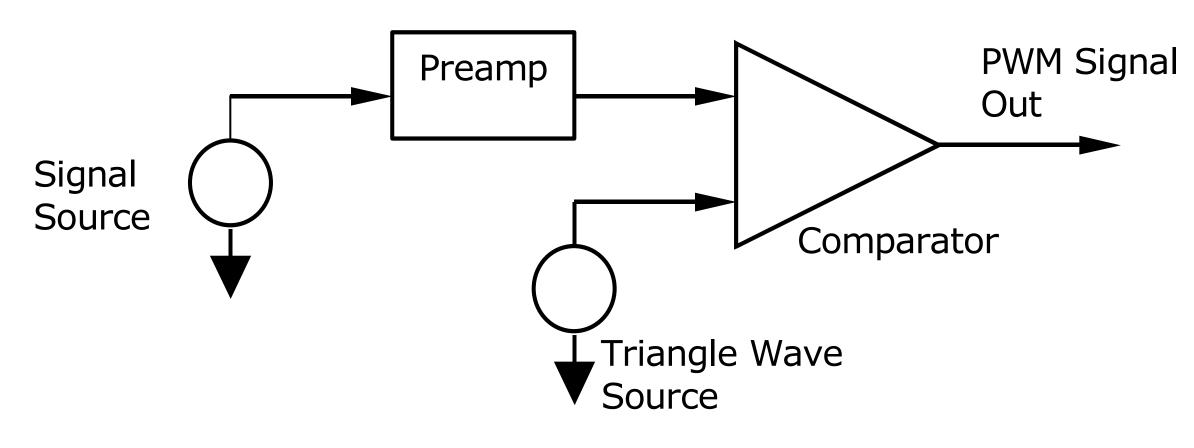

The Class-D amplification method offers design and consequently in simplicity in construction. Compared to other design classes, the Class-D design provides higher efficiency in a smaller enclosure. This class-D design is implemented in a 0.5 micron CMOS process. The design accepts as input a stereo signal from an audio source, such as a CD player, and provides as output, a "pulse-width modulated" signal to an Hbridge drive circuit, which is in turn used to drive a loudspeaker.

## **Department of Electrical and Computer Engineering Microelectronics Design and Simulation Laboratory**

# **Class-D Amplifier Front End** Steven E. Turner & Wayne H. Slade Jr.

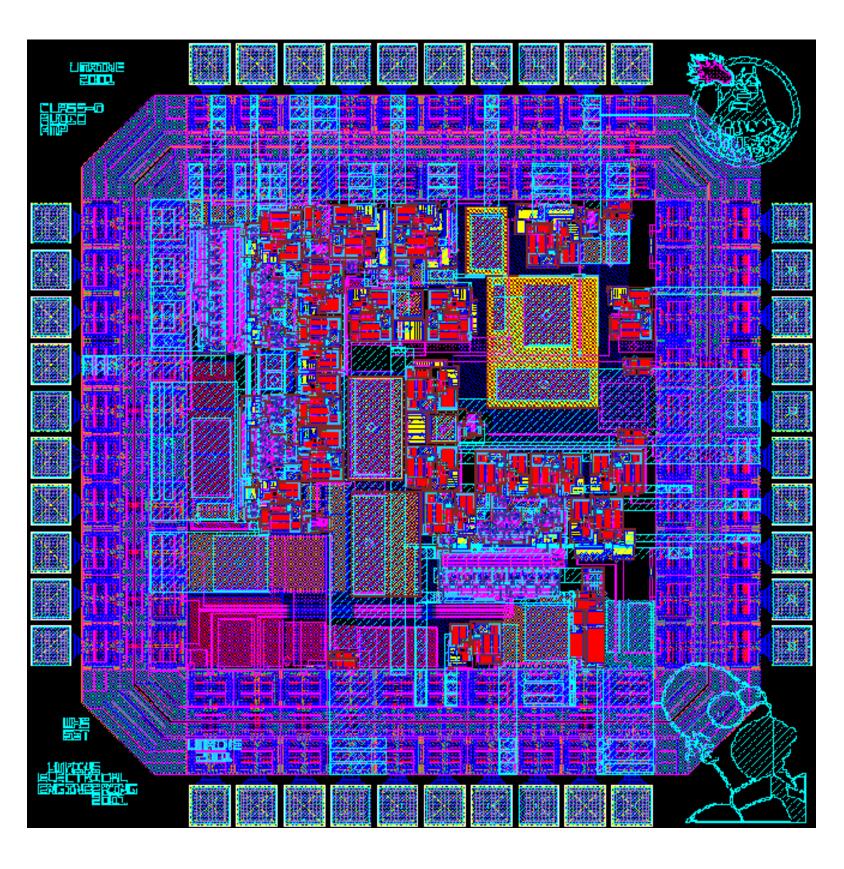

Circuit Design was performed using Cadence circuit design and simulation software, by Cadence Design Systems Inc. The design was sent to MOSIS and fabricated at an AMI foundry using the C5N CMOS process. This process is a 5 volt, L=0.5micron, 3 metal process, defined by 17 masks.

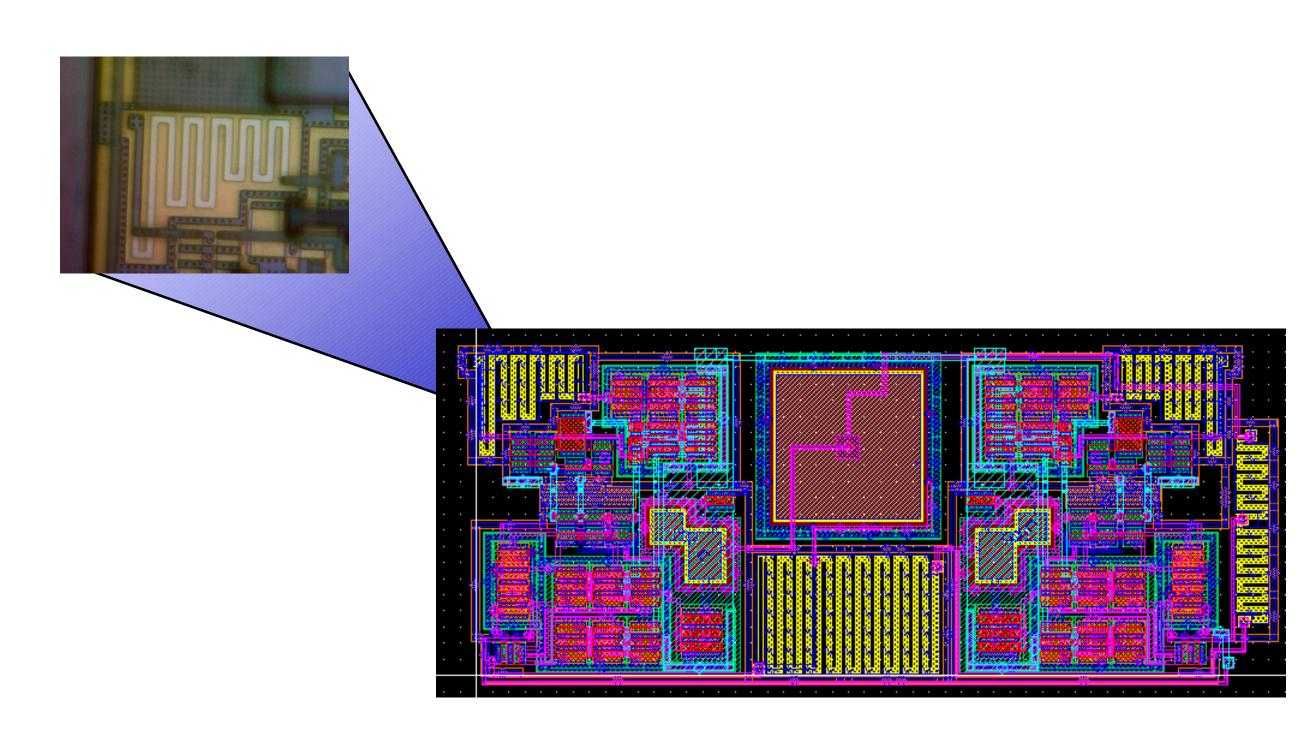

Microphotograph of 20k-ohm resistor (left) Layout view of wide-swing op-amp (right)

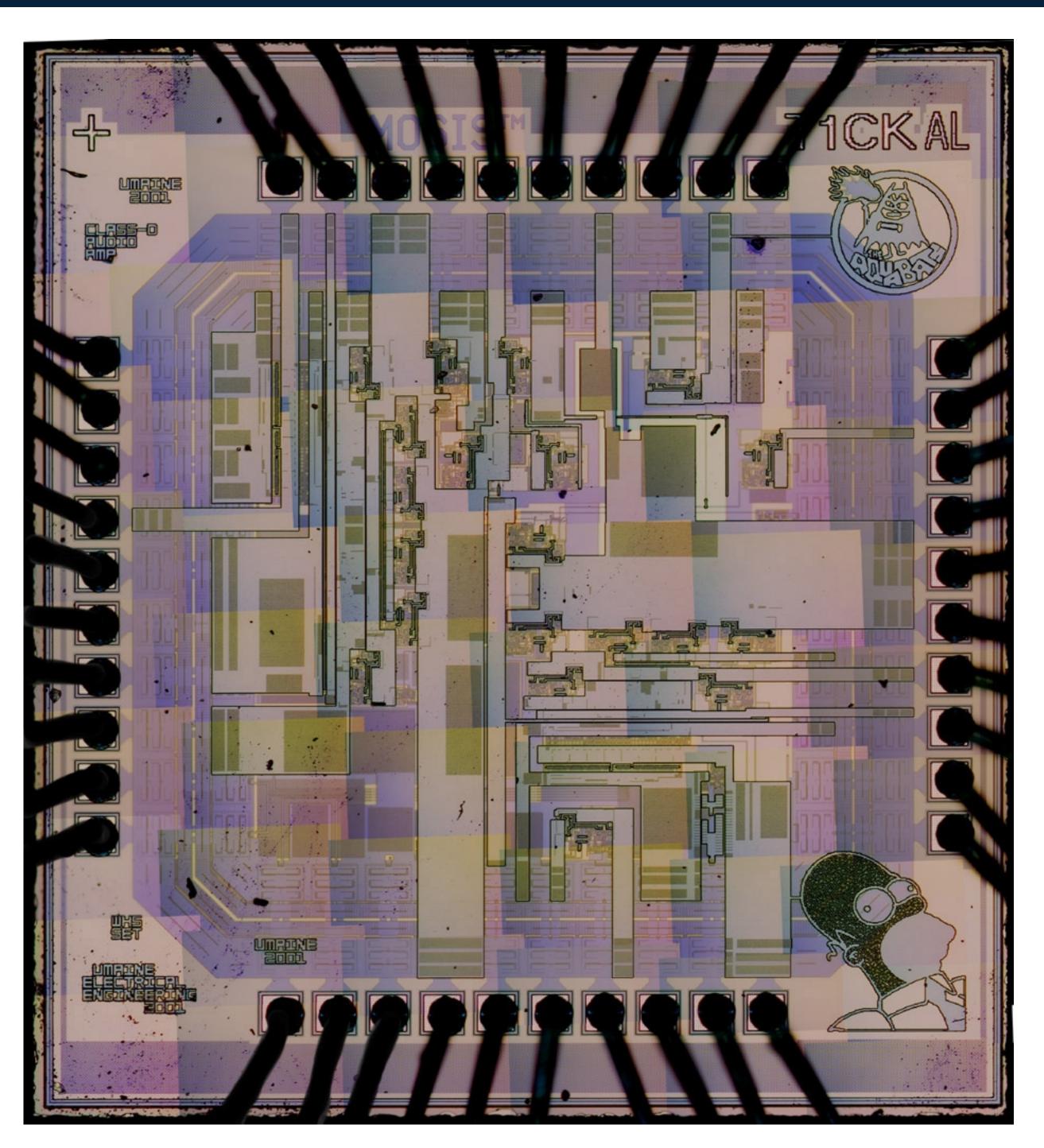

Microphotograph collage of circuit, 200x magnification (actual size 1.5 x 1.5 mm)

## System Components & Features

•Bistable Oscillator (Triangle and Square Wave)

- Comparator

- •Wide Swing Operational Amplifier

- Analog Comparator

- Digital Volume Control

- •Input Buffers

- •ESD Protection

- •Test and Characterization Circuits

Component level schematic

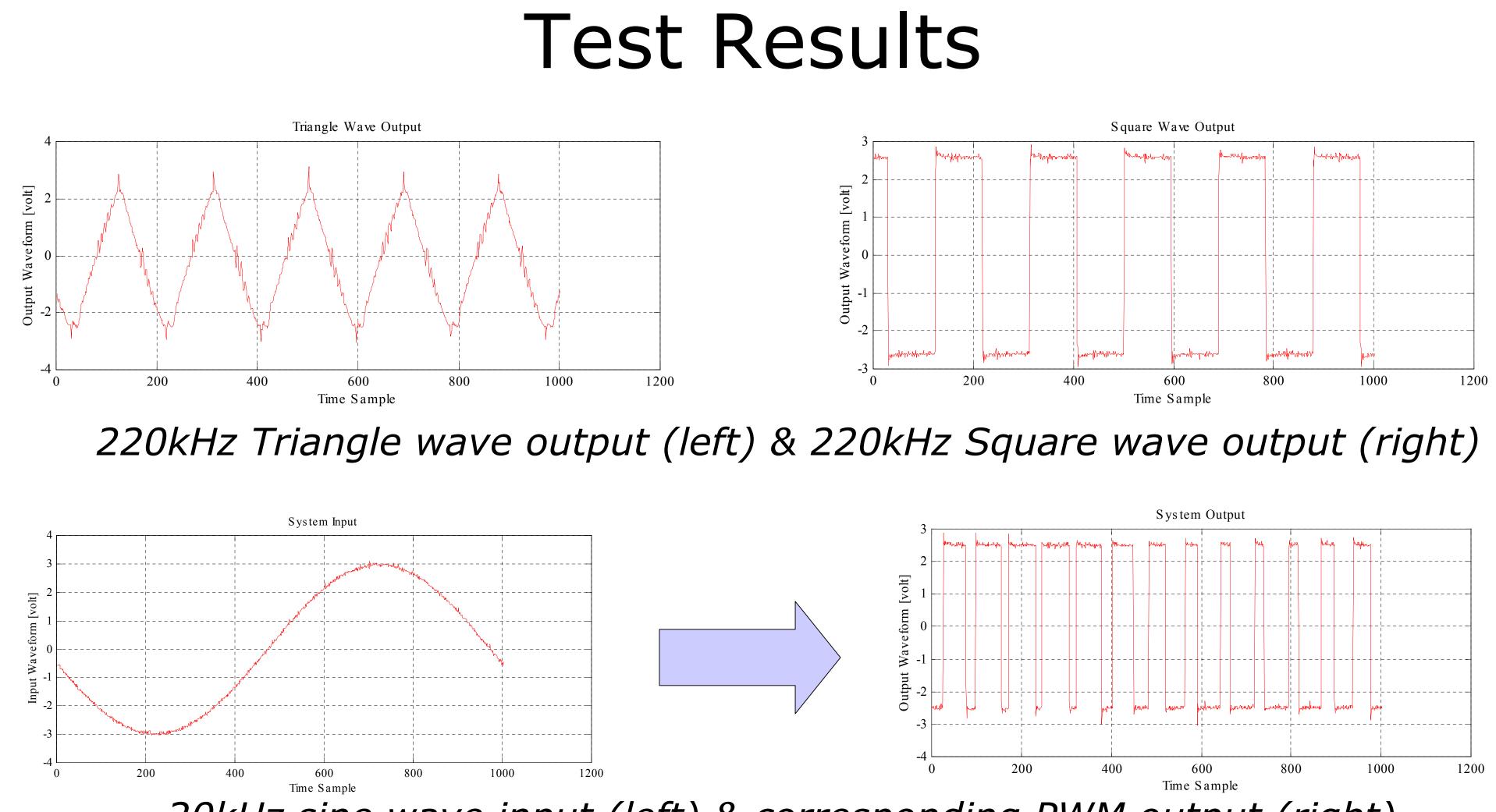

20kHz sine wave input (left) & corresponding PWM output (right)

1 8 6 5

**THE UNIVERSITY OF**