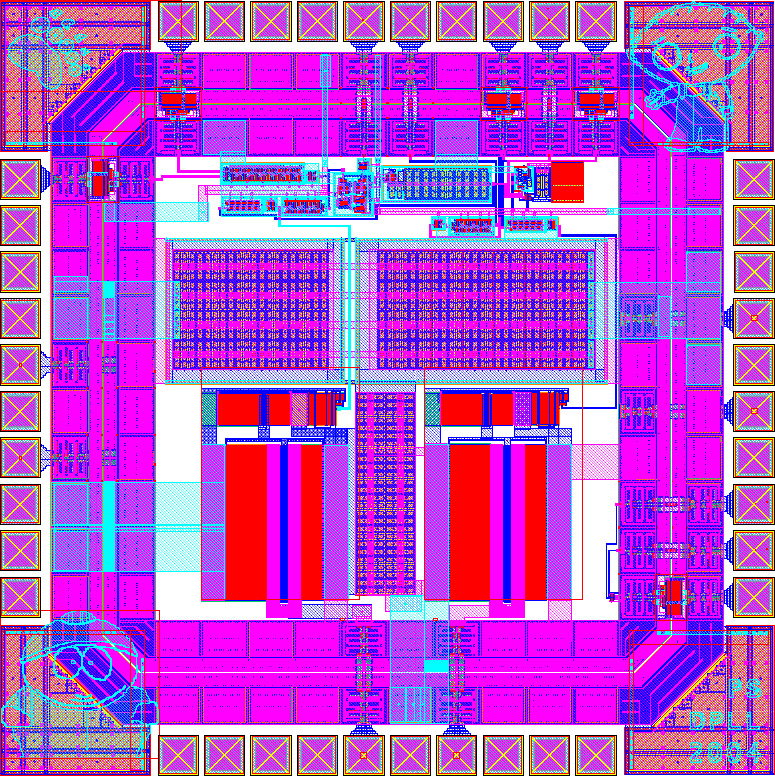

320MHz Digital Phase Locked Loop

A project for ECE 547 "VLSI Design" - Fall Semester 2004

Department of Electrical and Computer Engineering

University of Maine

Designed by: Patrick Spinney

DPLLs (Digital Phase Locked Loop) are commonly used in communications systems. As part of an investigation into RFID technology, a DPLL suitable for low-cost, low-power applications is designed and layed out out in a 0.5um CMOS process. It consists of a phase frequency detector, charge-pump filter, current-starved VCO, and a frequency divider. It is designed to operate using a reference signal between 10MHz and 46MHz producing an output signal between 80MHz and 368MHz (nominal inout of 40MHz yeilds an output frequency of 320MHz). The DPLL is part of a three chip RFID transceiver systems and generates additional signals (10MHz, 0.625MHz and lock enable) for use in the system.

The project report contains a description of the project, details of the design, simulation results, and layout.