10-Bit 5MHz Pipeline A/D Converter

A project for ECE 547 "VLSI Design" - Fall Semester 2002

Department of Electrical and Computer Engineering

University of Maine

Designed by: Kannan Sockalingam and Rick Thibodeau

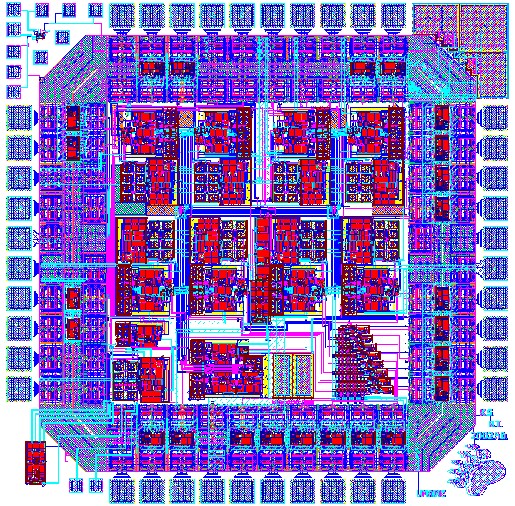

This ECE547 VLSI Design project consists of a 10-bit, 5MHz, pipeline architecture, analog to digital converter. The converter is implemented with a 9 stage pipeline architecture. The design is based on switch-capacitor circuitry. Each stage consists of an OTA, differential comparators(sub-ADC) and a sub-DAC. The converter accepts 0-1V (2.5V offset) fully differential signal up to 2.5MHz. The 1.5 bits/stage output is digitally corrected to obtain a 10 bit ADC output. MOSIS implements the device in AMI's C5N process technology. The 0.5 micron minimum gate length is physically designed on a 0.15 micron grid. This constrains the gate length to a minimum of 0.6 microns. The die size is 1.5 X 1.5 microns and will be packaged in a 40 pin DIP.

The project report contains a description of the project, details of the design, and test results. Details of the layout are shown in Appendix B. A poster describing our project is also available.