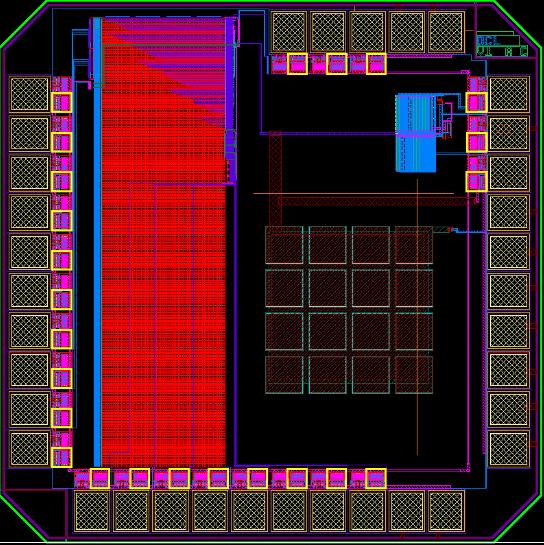

1kB Static Random Access Memory (SRAM)

A project for ECE 547 "VLSI Design" - Fall Semester 2013

Department of Electrical and Computer Engineering

University of Maine

Designed by: Donald Lewis

The design, simulation, and layout of an Asynchronous 1KB SRAM is presented. The SRAM is constructed from four 256 byte blocks and is built on a 180nm process and uses 3.3V devices.

The project report contains a description of the project and details of the design and layout.