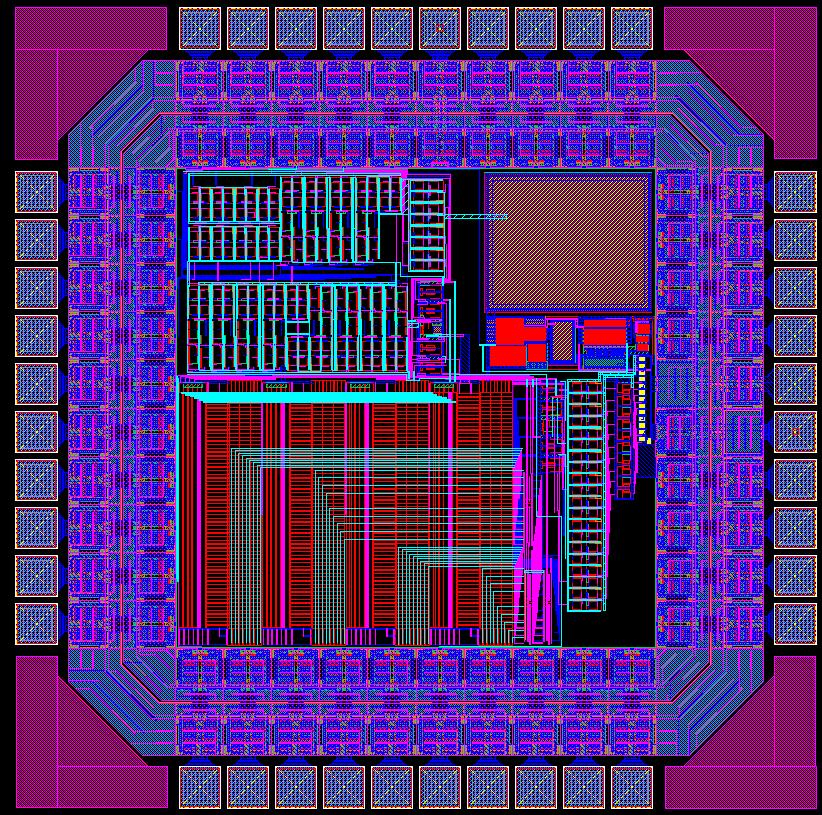

10-bit D/A Converter for a 50MHz Direct Digital Synthesizer

A project for ECE 547 "VLSI Design" - Spring Semester 2006

Department of Electrical and Computer Engineering

University of Maine

Designed by: Steve Fortune

This IC generates a 25MHz sinusoidal waveform centered at 2.55V with an amplitude of 0.85V (Vpp = 1.7V) when given a 12-bit binary input that count from 000h through FFFh with transitions occuring at 50MHz. The major design blocks include a 12-bit Accumulator, 8-bit ROM Pointer, 4x64-bit ROM and a 10-bit DAC. See schematic in Figure 2 in the project report.

Complete project details are available in the project report.