Frequency Selective MASH IQ Sigma Delta Modulator

A project for ECE 547 "VLSI Design" - Fall Semester 2001

Department of Electrical and Computer Engineering

University of Maine

Designed by: Ron Bryant and Scott Saucier

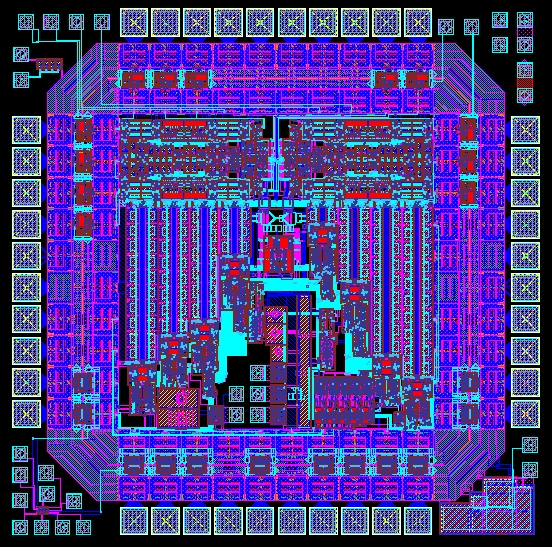

This chip contains two fourth-order MASH architecture switched capacitor sigma-delta ADCs, one channel each for the in-phase and quadrature parts of the signal. The input signal is translated in frequency by a switched capacitor network, which alternates the sampling capacitor used by the first loop of the converter. This allows the user to choose the frequency band of the input signal that will be converted with the best resolution by the loop. The digital filters recombine the bits from each stage in the MASH architecture which helps to remove error generated in the first stage. The converter runs at a maximum sampling frequency of 5MHz, and the input signal is converted in sections of Fs/32. The recombined outputs from two chips run in parallel will be used to convert a larger portion of the input spectrum.

The project report contains a description of the project, details of the design and layout, and test results. A poster describing our project is also available.